- 您现在的位置:买卖IC网 > Sheet目录3882 > PIC16F77T-I/ML (Microchip Technology)IC MCU FLASH 8KX14 A/D 44QFN

Micrel, Inc.

KSZ8851-16MLLJ

March 2010

43

M9999-030210-1.0

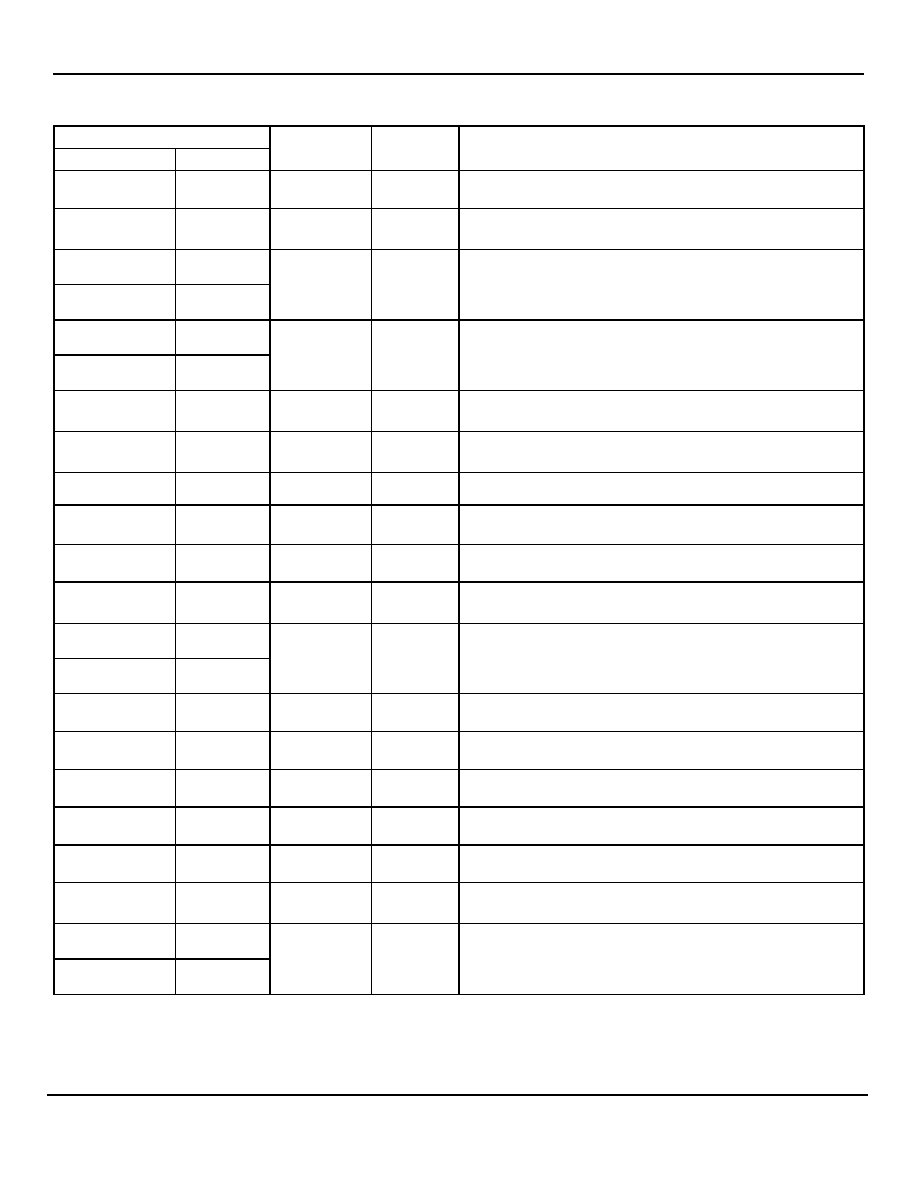

Internal I/O Registers Space Mapping (Continued)

I/O Register Offset Location

16-Bit

8-Bit

Register

Name

Default

Value

Description

0xB4 - 0xB5

0xB4

0xB5

FCOWR

0x0040

Flow Control Overrun Watermark Register [7:0]

Flow Control Overrun Watermark Register [15:8]

0xB6 - 0xB7

0xB6

0xB7

Reserved

Don’t care

None

0xB8 - 0xB9

0xB8

0xB9

0xBA - 0xBB

0xBA

0xBB

Reserved

Don’t care

None

0xBC - 0xBD

0xBC

0xBD

0xBE - 0xBF

0xBE

0xBF

Reserved

Don’t care

None

0xC0 - 0xC1

0xC0

0xC1

CIDER

0x8870

Chip ID and Enable Register [7:0]

Chip ID and Enable Register [15:8]

0xC2 - 0xC3

0xC2

0xC3

Reserved

Don’t care

None

0xC4 - 0xC5

0xC4

0xC5

Reserved

Don’t care

None

0xC6 - 0xC7

0xC6

0xC7

CGCR

0x0835

Chip Global Control Register [7:0]

Chip Global Control Register [15:8]

0xC8 - 0xC9

0xC8

0xC9

IACR

0x0000

Indirect Access Control Register [7:0]

Indirect Access Control Register [15:8]

0xCA - 0xCB

0xCA

0xCB

Reserved

Don’t care

None

0xCC - 0xCD

0xCC

0xCD

0xCE - 0xCF

0xCE

0xCF

Reserved

Don’t care

None

0xD0 - 0xD1

0xD0

0xD1

IADLR

0x0000

Indirect Access Data Low Register [7:0]

Indirect Access Data Low Register [15:8]

0xD2 - 0xD3

0xD2

0xD3

IADHR

0x0000

Indirect Access Data High Register [7:0]

Indirect Access Data High Register [15:8]

0xD4 - 0xD5

0xD4

0xD5

PMECR

0x0080

Power Management Event Control Register [7:0]

Power Management Event Control Register [15:8]

0xD6 - 0xD7

0xD6

0xD7

GSWUTR

0X080C

Go-Sleep & Wake-Up Time Register [7:0]

Go-Sleep & Wake-Up Time Register [15:8]

0xD8 - 0xD9

0xD8

0xD9

PHYRR

0x0000

PHY Reset Register [7:0]

PHY Reset Register [15:8]

0xDA - 0xDB

0xDA

0xDB

Reserved

Don’t care

None

0xDC - 0xDD

0xDC

0xDD

0xDE - 0xDF

0xDE

0xDF

Reserved

Don’t care

None

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC18F24K20-I/SS

IC PIC MCU FLASH 8KX16 28SSOP

PIC16F77-E/ML

IC MCU FLASH 8KX14 A/D 44QFN

PIC16LF74T-I/ML

IC MCU FLASH 4KX14 A/D 44QFN

PIC16F723-I/MV

IC MCU 8BIT 7KB FLASH 28UQFN

PIC18F442T-I/ML

IC MCU FLASH 8KX16 EE A/D 44QFN

PIC18LF2439-I/SP

IC MCU FLASH 6KX16 EE A/D 28DIP

PIC16F687-I/ML

IC PIC MCU FLASH 2KX14 20QFN

PIC18LF2439-I/SO

IC MCU FLASH 6KX16 EE A/D 28SOIC

相关代理商/技术参数

PIC16F77T-I/PT

功能描述:8位微控制器 -MCU 14KB 368 RAM 33 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F77T-I/PTG

功能描述:8位微控制器 -MCU 14KB 368 RAM 33 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F77TIPT

制造商:MICROCHIP 功能描述:New

PIC16F785-E/ML

功能描述:8位微控制器 -MCU 3.5 KB 128 RAM 18I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F785-E/P

功能描述:8位微控制器 -MCU 14KB 368 RAM 33 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F785-E/SO

功能描述:8位微控制器 -MCU 3.5KB FL 128R 18 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F785-E/SS

功能描述:8位微控制器 -MCU 3.5KB FL 128R 18 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F785-I/ML

功能描述:8位微控制器 -MCU 3.5 KB 128 RAM 18I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT